|

Структурная интерпретация конвейеров.

|

|

|

|

Если имеем набор задач L.

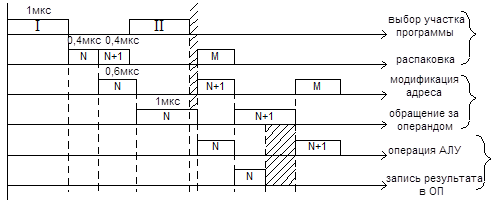

Выбирая длину конвейера, при условии наличия больших программ, способных загрузить конвейер, можно добиться того, что в каждом такте процессора Тц будем получать результат одной команды. В результате длительность выполнения любой операции, независимо от ее длины (короткая- сложение или длинная - умножение) составит 1 такт, что имеет место в современных процессорах.

Выбирая длину конвейера, при условии наличия больших программ, способных загрузить конвейер, можно добиться того, что в каждом такте процессора Тц будем получать результат одной команды. В результате длительность выполнения любой операции, независимо от ее длины (короткая- сложение или длинная - умножение) составит 1 такт, что имеет место в современных процессорах.

Например, производительность процессора i860 при частоте 40МГц составляет 80 миллионов операций в секунду.

Структурная схема конвейерного

Процессора машин III поколения.

До внедрения синхронной технологии на базе микропроцессоров наибольшее распространение имел асинхронный способ обработки информации. Например, в машине ЕС 1050 одновременно выполнялись 3 команды. Это стало возможным благодаря низкому уровню обобществления оборудования ядра процессора.

1-й уровень реализует выборку фрагмента программы из ОП, длина слова которой – 8байт. Выделение команды из слова ОП и размещение ее в регистре команд называется распаковкой.

2-й уровень – формирование адресов операндов; выборка их из регистровой или оперативной памяти и размещение в специальных регистрах центрального устройства управления.

3-й уровень – выполнение действий над операндами в АЛУ и запись результатов в местную или оперативную память. Каждый уровень процессора составляет функционально независимые узлы (блоки). Совокупность узлов обеспечивающих выполнение одновременно 3-х команд называется центральным узлом процессора (управления).

БВК – блок выборки команд

БВК – блок выборки команд

БВД – блок выборки данных

БСА – блок сумматора адреса

БАР – блок адреса результата

|

|

|

ЦУУ – центральное устройство управления

Каждый уровень использует 2триггера (триггер готовности и триггер занятости) для обеспечения асинхронного обмена.

|

Пример совмещения циклов для обработки команд формата RX:

Время задержки в АЛУ определяется командой. Заштрихованные области – простой блока.

В ЕС 1061 для ускорения выполнения операций используется порядка 8-ми постпроцессоров – арифметических расширителей системы команд.

Табличные процессоры.

Появление запоминающих микросхем большой ёмкости и с высоким быстродействием сделало возможным построение процессора на основе запоминающих устройств (ЗУ), которые используются как таблица соответствия входных операндов результату операций.

Структура табличного процессора.

Структура табличного процессора.

Поле адреса А условно разделим пополам на А и В.

Поле адреса А условно разделим пополам на А и В.

Количество ячеек: N=2(Am+Bm),

где Аm и Вm максимальные значения входа.

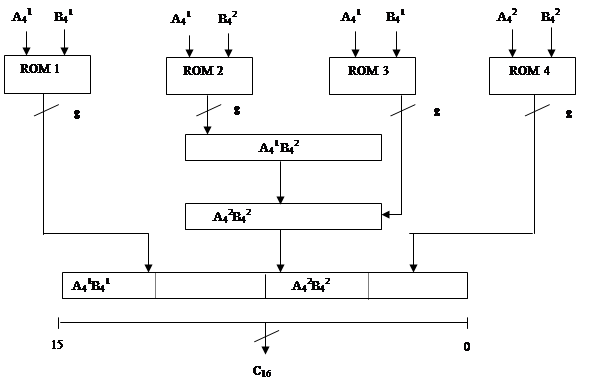

Пример табличного процессора для операции умножения.

Можно реализовать операции сложение, вычитание, деление, синус и другие.

Можно реализовать операции сложение, вычитание, деление, синус и другие.

Недостаток табличного процессора: ёмкость запоминающих микросхем табличного процессора резко возрастает с увеличением разрядности операндов.

Два варианта построения табличного процессора на запоминающих микросхемах малой ёмкости.

1. Использование табличного процессора для вычисления значений операций в ключевых (опорных) точках, а значения между ключевыми точками вычисляются с помощью аппроксимации (интерполяционные методы вычисления) или с помощью итерационного метода- метод последовательных приближений.

2. Алиготивные методы: когда операнд можно разбить на части и выполнять операции над частями операндов, имеющих меньшую разрядность.

Построение табличного процессора для (А8*В8)=C16.

Разобьём на составляющие: (А41*24+ А42)=А8 и (В41*24+В42)=В8,

где А41, В41-старшие 4 разряда;

|

|

|

А42, В42-младшие 4 разряда.

(А41*24+ А42)(В41*24+В42)= А41* В41*28+24(А41* В42+ А42* В41)+ А42* В42= C16

|

tоп=tсч+2tсум» 3t

tоп -время операции; tсч -время считывания; tсум -время суммирования.

Все четыре запоминающие микросхемы одинаковые, следовательно можно использовать только одну вместо четырёх. Это приведёт к увеличению времени выполнения за счёт снижения количества оборудования. Аналогично реализуются табличные процессоры и для других операций.

|

|

|