|

IM – автоматы с последовательной комбинационной частью.

|

|

|

|

|

S – автоматы.

Пунктиром выделена дополнительная загрузка. КС сосредоточена в одном месте, есть ЗУ для массивов информации.

Работа автомата: по управляющим сигналам а1 и а2 числа записываются в S1 и S2, а по сигналам b1 и b2 передается на вход КС. Управляющий сигнал jк осуществляет выбор одной из м/о, реализуемой КС. В 1-ом такте по адресу А число выбирается в S1 из ЗУ, во втором такте – из ЗУ в S2. В третьем такте содержимое обоих регистров S1 и S2 (или одного из них) поступает на вход КС. Результат дописывается в ЗУ. Главная задача: сокращение тактов на выполнение одной м/о. Для этого: 1)вводят дополнительные регистры S3...Sm, чтобы совместить такт выборки слова из ЗУ с исполнением очередной м/о; 2)вводится дополнительная загрузка, S2 – итоговый регистр (аккумулятор); 3)содержимое ЗУ подается на вход КС минуя элементы памяти.

В общем случае м/о реализуется за 3 такта, а введение указанных способов ускорения снижает время выполнения до 2-х и 1-го тактов.

На характеристики ОА существенным образом влияют:

1. Линии связей.

2. Тактирование ОА.

1.1 Линии связей магистрального типа.

Достоинства: а) простота; б)малые затраты оборудования.

Достоинства: а) простота; б)малые затраты оборудования.

Недостатки: а) в каждый момент времени информация передается между одним источником и одним или несколькими получателями.

Если разрядность шины 32, Fцикла =100МГц, то пропускная способность шины Jш=32/Тц=32*Fцикла=32*100*106=3,2 (Гбита/сек)=400 (Мбайт/сек).

Для увеличения скорости обмена в ОА используются несколько магистралей.

В машинах III поколения использовали 3 и более шин; в машинах IV поколения: IBM PC/XT – 3 магистрали (шины), IBM PC/AT – 6 магистралей (шин). Введение дополнительных магистралей увеличивает количество передач в единицу времени.

|

|

|

б) каналы магистрального типа имеют большую емкостную нагрузку, что снижает возможность повышения тактовых частот.

в) поскольку магистрали – универсальные линии связи, и она должна обладать функциональной полнотой, то по структуре она оказывается достаточно сложной.

1.2 Линии связи непосредственного типа.

1) Линии связи устанавливаются содержательными микропрограммами.

2) В каждый момент времени можно одновременно передать данные между несколькими группами устройств. Например, S1->S2 и S3->S4 (S2->S3 и S4->S1).

3) Для увеличения количества передач в качестве элементов памяти используют 2-х ступенчатые триггеры (МS регистры – Master/Slave), а также промежуточные конвейерные регистры.

4) Структурно непосредственные связи проще магистралей и по числу линий и по временным диаграммам обмена.

Тактирование ОА

TОА=tУАtОА – такт ОА.

WОА=Nм/о /TОА – производительность.

I автомат: каждый элемент памяти имеет свою КС, поэтому он имеет наибольшее число м/о выполняемых за один такт.

Все м/о можно разделить на совместимые, те которые могут выполняться одновременно и несовместимые. Например, записать в S1 число и произвести его сдвиг невозможно одновременно. Поэтому включать их в одну микрокоманду нельзя. Несовместимые м/о можно сделать совместимыми разнеся их по разным тактам управляющих сигналов. Такое тактирование называется многофазным.

В машинах III поколения такт работы процессора четырехфазный Tпроц.=t1+t2+t3+t4. В машинах IV поколения Tпроц=Ti+...+Ti+T1+T2+T3+Tw+...+Tw+T4+Ti,где Тi- холостые синхроимпульсы в режиме ожидания, прерывания, останова; T1,T2,T3,T4 – рабочие синхроимпульсы; Тw – импульсы ожидания определяемые скоростью внешнего устройства.

Методы повышения производительности процессоров.

1) Конвейерные процессоры.

2) Векторные процессоры.

3) Скалярные процессоры.

|

|

|

4) Суперскалярные процессоры.

Конвейерные процессоры

Принципы совместимости операций предложил академик Лебедев в 1956 году.

Время цикла Тпр=t1+t2+t3+t4+t5 (1), где t1 – выборка команды; t2 – формирование исполнительных адресов; t3 – выборка операндов; t4 – выполнение операции и запись результата; t5 – обработка прерываний.

Если все операции выполняются последовательно на одном операционном автомате, то Ткоманды=åti (1), где i=1..5 для нашего случая. Производительность Wк=1/Tk=1/åti (2). Анализируя выражения 1 и 2: аппаратные затраты невысоки за счет высокой совместимости узлов процессора.

Лебедевым был предложен принцип совместимости когда он использовал несколько ОА. Например, в машине М20 использовалось 5 ОА.

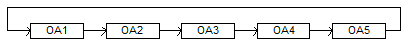

Последовательность выполнения микроопераций:

1 1 - - - -

2 2 1 - - -

3 3 2 1 - -

4 4 3 2 1 -

5 5 4 3 2 1

Начиная с пятого такта процессор обрабатывает одновременно 5 команд. Для каждой команды время выполнения - ti. Производительность повышается примерно в 5 раз, но в общем случае ti¹tj (i¹j). Возникает проблема синхронизации.

Различают два типа конвейеров:

1) Синхронный конвейер. Тцикла=max ti (3),где i=1..5, при этом возникают различные ситуации:

А) ti+tj>Tц (4). Если данное условие не выполняется, то данные микропрограммы i и j объединяются и реализуются на одном ОА.

В) Когда tp>>ti+ti (4’), тогда tp делится на tp1 и tp2 и реализуется на разных ОА.

Выражения 4 и 4’ обеспечивают сокращение времени простоя при постоянном цикле. Главная задача выровнять ti. Производительность из-за простоев уменьшается и значительно.

2) Асинхронные конвейерные ОА.

Каждый уровень конвейера содержит триггер готовности и триггер занятости. Триггер занятости(Тз) устанавливается в 1 если он занят обработкой текущей микропрограммы и не может принять информацию предыдущего уровня. Триггер готовности (Тг) устанавливается в 1 если обработка, выполнение микропрограммы закончена и готов передать данные в ОА следующего уровня. Тогда условия передачи информации с одного уровня на другой можно показать так: Tг(i)=1;Тз(i+1)=0.

Широко применяются конвейеры с асинхронным способом передачи. Данные режим получил название «Квитирование» – запрос с подтверждением.

|

|

|