|

Синтез комбинационных схем на мультиплексорах

|

|

|

|

Кроме основного назначения (коммутация сигналов) мультиплексоры используют для построения постоянных запоминающих устройств (ПЗУ) объемом 2m+1 бит и для синтеза комбинационных логических схем. При этом можно синтезировать  различных логических функций от (m+1) логических переменных. Например, на мультиплексоре с n=4 и m=2 входами реализуется любая логическая функция от трех переменных, т.к. для трех переменных существует

различных логических функций от (m+1) логических переменных. Например, на мультиплексоре с n=4 и m=2 входами реализуется любая логическая функция от трех переменных, т.к. для трех переменных существует  различных функций.

различных функций.

При построении ПЗУ на информационные входы мультиплексора подают не изменяющиеся во времени сигналы 0 и 1. Считывание данных сигналов производится подачей соответствующих сигналов на адресные (управляющие) входы.

В этом случае мультиплексор реализует некоторую наперед заданную функцию, представленную в совершенной дизъюктивной нормальной форме (СДНФ), как следует из представленной выше логической функции мультиплексора.

Основной задачей при синтезе комбинационных логических схем на мультиплексорах является оптимальный выбор переменных, подаваемых на его управляющие (адресные) входы.

Критерием оптимальности выбора адресных переменных может служить количество сигналов 0 и 1, подаваемых при этом на информационные входы.

Правило выбора адресных переменных рассмотрим для двух случаев.

Пусть логическая функция задана табл.5.3

Таблица 5.3

Таблица истинности

| х1 | х2 | х3 | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Выделим из логических переменных переменную х3. Одинаковые комбинации оставшихся переменных х1 х2 представим в виде групп (отделены в таблице истинности двойными горизонтальными линиями).

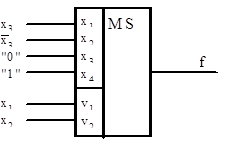

Выберем в качестве адресных (управляющих) переменных переменные х1 и х2. При коде v1v2=x1x2=00 на выход мультиплексора коммутируется вход Х1. Если на вход Х1 подать переменную х3, то на выходе получим значение логической функции при х1х2=00. Это удобно отразить в табл.5.4

|

|

|

Таблица 5.4

Таблица истинности

Адресные переменные | Информационные переменные | Выход | ||||

| v1 x1 | v2 x2 | X1 | X2 | X3 | X4 | f |

| 0 | 0 | x3 | x3 | |||

| 0 | 1 |

|

| |||

| 1 | 0 | 0 | 0 | |||

| 1 | 1 | 1 | 1 | |||

При коде v1v2=x1x2=01 на выход коммутируется вход Х2. В соответствии с таблицей истинности логической функции, на этот вход следует подать  .

.

При коде v1v2=x1x2=10 на выход коммутируется вход x3. В соответствии с таблицей истинности логической функции, на этот вход следует подать "0".

При коде v1v2=x1x2=11 на выход коммутируется вход x4. В соответствии с таблицей истинности логической функции, на этот вход следует подать "1" (рис. 5.2).

|

|

Рис. 5.2 Пример синтеза комбинационной схемы на мультиплексоре.

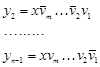

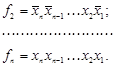

На мультиплексорах можно реализовывать совместно две функции. При этом отыскивают те переменные, которые суммарно входят в МДНФ функций наибольшее число раз. Например, заданы МДНФ двух функций:

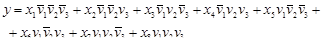

.

.

Таблица истинности для них выглядит следующим образом:

| x1 | x2 | x3 | x4 | f1 | f2 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

Если в качестве таких переменных выбрать х3 и х2, то получим следующие таблицы истинности для заданных функций.

Для f1:

| v1 x3 | v2 x2 | X1 | X2 | X3 | X4 | f1 |

| 0 | 0 |

|

| |||

| 0 | 1 |

|

| |||

| 1 | 0 |

|

| |||

| 1 | 1 |

|

|

Для f2:

| v1 x3 | v2 x2 | Y1 | Y2 | Y3 | Y4 | f2 |

| 0 | 0 |

|

| |||

| 0 | 1 | 0 | 0 | |||

| 1 | 0 |

|

| |||

| 1 | 1 |

|

|

|

|

|

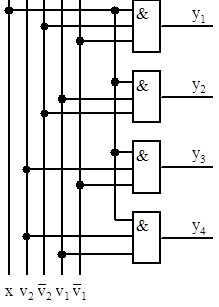

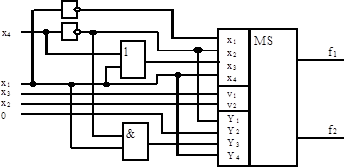

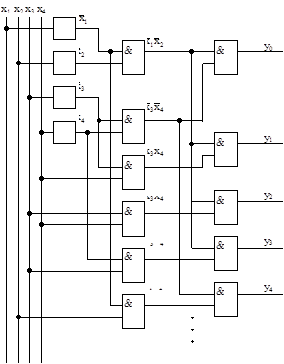

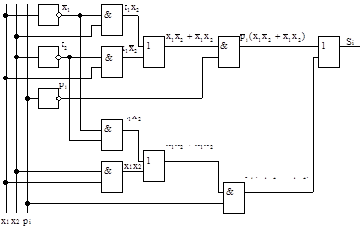

Функциональная схема устройства на сдвоенном четырехканальном мультиплексоре имеет вид рис.5.3.

Рис. 5.3 Применение мультиплексора для реализации совместно двух логических функций.

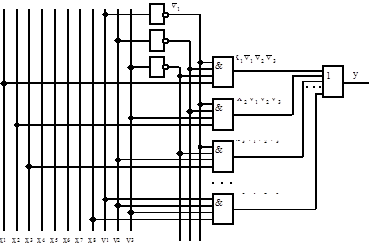

Пример 5.1. Синтезировать мультиплексор с восемью информационными входами и одним выходом на элементах И, ИЛИ, НЕ.

Решение. 1. Восемь информационных входов могут коммутироваться на один выход с помощью трех адресных входов (n=2m, для n=8, m=3) 2. Таблица истинности для логической функции мультиплексора (табл. 5.5).

Таблица 5.5

Таблица истинности

| Адрес | Выход y | ||

| v1 | v2 | v3 | |

| 0 | 0 | 0 | x1 |

| 0 | 0 | 1 | x2 |

| 0 | 1 | 0 | x3 |

| 0 | 1 | 1 | x4 |

| 1 | 0 | 0 | x5 |

| 1 | 0 | 1 | x6 |

| 1 | 1 | 0 | x7 |

| 1 | 1 | 1 | x8 |

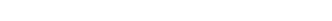

3. Логическая функция в соответствии с таблицей истинности:

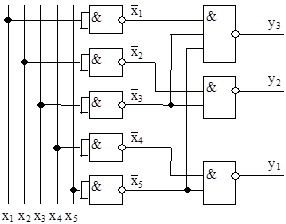

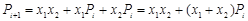

4. Функциональная схема мультиплексора рис.5.4.

Рис 5.4 Функциональная схема мультиплексора с восемью информационными входами.

Демультиплексоры

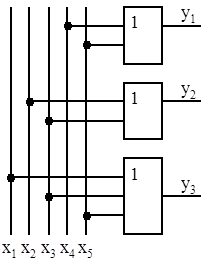

Демультиплексор - комбинационное устройство с одним информационным входом х1, с m управляющими входами (v1...vm) и с n информационными выходами (y1...yn), при этом n=2m.

Основное назначение демультиплексора - распределение сигнала с линии по нескольким каналам (обратное мультиплексору).

Таблица истинности для n=8 и m=3 (табл.5.6)

Таблица 5.6

Таблица истинности для n =8 и m =3

| v3 | v2 | v1 | y1 | y2 | y3 | y4 | y5 | y6 | y7 | y8 |

| 0 | 0 | 0 | x | |||||||

| 0 | 0 | 1 | x | |||||||

| 0 | 1 | 0 | x | |||||||

| 0 | 1 | 1 | x | |||||||

| 1 | 0 | 0 | x | |||||||

| 1 | 0 | 1 | x | |||||||

| 1 | 1 | 0 | x | |||||||

| 1 | 1 | 1 | x |

где х принимает значение 0 или 1.

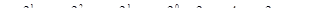

Работа демультиплексора описывается уравнениями:

Функциональная схема демультиплексора, построенного по этим уравнениям для n=4, m=2 (рис.5.5).

|

|

Рис 5.5 Функциональная схема демультиплексора с четырьмя выходами.

Дешифраторы

Полным дешифратором называют комбинационную схему, имеющую n входов и 2n выходов и реализующую на каждом выходе функцию, представляющую собой минтерм n переменных.

Дешифраторы являются преобразователями кодов, выполняющих преобразование двоичного и двоично-десятичного кодов в унитарный код. Унитарный код двоичного n-разрядного числа представляется 2n разрядами, только один из разрядов которого равен 1 [6].

|

|

|

Поэтому в полном дешифраторе каждой комбинации значений входных сигналов х1,..., хn соответствует сигнал, равный 1, только на одном выходе, на остальных выходах сохраняются сигналы 0. На выходах вырабатываются 1 при минтермах соответственно:

Такой системе уравнений, например, для n=2 соответствует табл.5.7.

Таблица 5.7. Таблица истинности

| х2 | х1 | f0 | f1 | f2 | f3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

Пример 5.2. Синтезировать преобразователь кода прямого замещения в двоично-десятичный код 2421.

Решение 1. Код прямого замещения представляет собой обычное представление одноразрядного десятичного числа в двоичной системе счисления, т.е.

2. Двоично-десятичный код 2421 соответствует представлению числа в виде

Таким образом, преобразователь кодов представляет собой схему с четырьмя входами и четырьмя выходами.

3. Составляют таблицу истинности для логической функции преобразователя кодов (табл.5.8).

Таблица 5.8

Таблица истинности преобразователя кодов

| Десятичное число | Код прямого замещения | Двоично-десятичный код 2421 на выходе | ||||||

| х1 | х2 | х3 | х4 | у1 | у2 | у3 | у4 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | ФУНКЦИЯ НЕ ОПРЕДЕЛЕНА | ||||

| 1 | 0 | 1 | 1 | |||||

| 1 | 1 | 0 | 0 | |||||

| 1 | 1 | 0 | 1 | |||||

| 1 | 1 | 1 | 0 | |||||

| 1 | 1 | 1 | 1 | |||||

4. Получают логическую функцию преобразователя кодов в виде СДНФ путем записи "по единицам", представленную системой уравнений:

5. Получают логическую функцию в виде МДНФ с помощью карт Карно рис.5.6

| х1х2 х3х4 | 00 | 01 | 11 | 10 |

| х1х2 х3х4 | 00 | 01 | 11 | 10 |

| 00 |  х х

| 1 | 00 |  1 1

|  х х

| 1 | ||||

| 01 |  1 1

| х | 1 | 01 | х | 1 | ||||

11 11

|  1 1

| х | х | 11 |  1 1

| х | х | |||

| 10 | 1 | х | х | 10 |  1 1

| х | х |

|

|

|

у1=х1+х2х3+х2х4

| х1х2 х3х4 | 00 | 01 | 11 | 10 | х1х2 х3х4 | 00 | 01 | 11 | 10 | |

| 00 |  х х

| 1 | 00 | х | ||||||

| 01 |  1 1

| х | 1 | 01 |  1 1

| 1 | х | 1 | ||

11 11

| 1 | х |  Х Х

| 11 | 1 | 1 | х | х | ||

| 10 | 1 | х | Х | 10 | х | х |

Рис. 5.6. Карты Карно.

у4=х4

Синтезируемая схема реализует четыре функции. Ее можно представить как простое объединение схем, реализующих каждую функцию отдельно. Но это не экономично. Целесообразно преобразовать совокупность этих функций к такому виду, чтобы реализующие их схемы содержали общие части, а схема с четырьмя выходами представляла собой единое целое.

Для выполнения этого условия, используя избыточные наборы входных переменных х1х2х3х4, которые отмечены на картах Карно крестиками, образуют минимальные покрытия для каждой из четырех функций, которые включали бы возможно больше однотипных объединений клеток на картах.

В итоге получают МНДФ логической функции:

у1=х1+х2х3+х2х4=х1+х2(х3+х4)

у4=х4

5. Функциональная схема устройства на рис.5.7.

Рис. 5.7 Функциональная схема преобразователя кода прямого замещения в двоично-десятичный код 2421.

Пример 5.3. Синтезировать дешифратор для преобразования двоично-десятичного кода в код, предназначенный для управления десятичным индикатором (дешифратор 4  10).

10).

Решение. 1. Двоично-десятичный код 2421 соответствует представлению числа в виде:

.

.

Поэтому дешифратор должен иметь четыре входа.

2. Для управления десятичным индикатором на выходе необходимо получить десятичное число, т.е. дешифратор должен иметь десять выходов.

Таким образом дешифратор представляет собой схему с четырьмя входами и десятью выходами. Составляют таблицу истинности для логической функции дешифратора (табл.5.9)

Таблица 5.9

Таблица истинности дешифратора

| Десятичное число | Двоично-десятичный код на входе | код на выходе | ||||||||||||

| х1 | х2 | х3 | х4 | у0 | у1 | у2 | у3 | у4 | у5 | у6 | у7 | у8 | у9 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | ФУНККЦИЯ НЕ ОПРЕДЕЛЕНА | ||||||||||

| 1 | 0 | 1 | 1 | |||||||||||

| 1 | 1 | 0 | 0 | |||||||||||

| 1 | 1 | 0 | 1 | |||||||||||

| 1 | 1 | 1 | 0 | |||||||||||

| 1 | 1 | 1 | 1 | |||||||||||

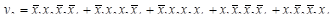

4. Получают логическую функцию дешифратора в виде СДНФ путем записи " по единицам":

|

|

|

|

|

5. При синтезе функциональной схемы следует учитывать, отдельные функции содержат общие части, поэтому схему с десятью выходами представляют как единое целое (рис.5.8)

Рис. 5.8 Функциональная схема дешифратора для преобразования двоично-десятичного кода в код, предназначенный для управления десятичными индикаторами (дешифратор 4  10)

10)

Шифраторы

Шифраторы выполняют функцию, обратную дешифраторам, т.е. преобразуют унитарный код в двоичный или двоично-десятичный.

Пример 5.4. Синтезировать шифратор на пять входов, выход которого представляется в двоичном коде.

Решение. 1. Шифратор преобразует унитарный код в двоичный или двоично-десятичный.

Унитарный код двоичного n-разрядного числа представляется 2n разрядами, только один из которых равен 1.

Шифратор имеет пять входов. Число 5 в двоичном коде представляется тремя разрядами: 101, т.е. шифратор должен иметь три выхода.

В соответствии с этим составляют табл.5.10

Таблица 5.10

Таблица истинности

| х1 | х2 | х3 | х4 | х5 | у1 | у2 | у3 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | ||||

| 1 | 0 | 1 | 0 | ||||

| 1 | 0 | 1 | 1 | ||||

| 1 | 1 | 0 | 0 | ||||

| 1 | 1 | 0 | 1 |

2. Получают логическую функцию шифратора в виде СДНФ путем записи "по единицам"

3. Функциональная схема шифратора в логическом базисе И-НЕ (рис.5.9.а) и в логическом базисе И, ИЛИ, НЕ (рис.5.9.б).

а).

б)

Рис. 5.9 Функциональная схема шифратора в логическом базисе И-НЕ (а) и в логическом базисе И, ИЛИ, НЕ (б)

Преобразователи кодов

Преобразователи кодов используют для шифрации и дешифрации цифровой информации и имеют n входов и m выходов. Соотношения между числами n и m могут быть любыми: n<>m.

Сумматоры

Сумматоры - это комбинационные устройства, осуществляющие суммирование чисел в двоичном коде.

Правила суммирования в простейшем случае - суммирования двух одноразрядных чисел, задаются таблицей двоичного сложения:

0+0=0

0+1=1

1+0=1

1+1=0+единица переноса в старший разряд.

Логическую функцию одноразрядного суммирования составляют на основании правил суммирования (табл. 5.11)

Таблица 5.11

Таблица истинности сумматора

Слагаемые | Результат суммирования | ||

| х1 | х2 | Si | Цифра переноса в старший разряд, рi+1 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Для получения логической функции одноразрядного суммирования в форме СДНФ производят запись " по единицам":

,

,

,

,

т.е. она реализуется двумя логическими функциями, а устройство имеет два выхода: Si и рi+1.

Схему, реализующую две функции, можно представить как простое объединение схем, реализующих каждую функцию отдельно, рис. 5.9:

Рис. 5.9 Функциональная схема одноразрядного сумматора: полусумматора.

Устройство оказывается синтезированным из двух самостоятельных частей, реализующих:

1) функцию исключающее ИЛИ (сумма по модулю два);

2) функцию конъюнкции И.

Такое устройство называется полусумматором.

Полный одноразрядный сумматор должен иметь вход для цифры переноса из предыдущего разряда рi и число слагаемых в нем оказывается равным трем: х1, х2, рi (табл.5.12). Логическую функцию для полного одноразрядного сумматора представляют таблицей истинности, составленной на основании правил суммирования.

Таблица 5.12

Таблица истинности полного одноразрядного сумматора

| Слагаемые | Результат суммирования | |||

| Цифра переноса из предыдущего Разряда рi | Первое слагаемое x1 | Второе Слагаемое x2 | Сумма Si | Цифра переноса в старший разряд, pi+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Для получения логической функции в алгебраической форме в виде СДНФ производят запись по "единицам":

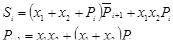

,

,

Далее производят минимизацию логических функций. Выражение для Si не поддается минимизации изложенными ранее методами. Единственная возможность - это использовать вынесение за скобки:

Для выражения рi+1 можно получить сокращенную дизъюнктивную нормальную формы применив все операции склеивания и поглащения:

1-4:  (по рi)

(по рi)

2-4:  (по х2)

(по х2)

3-4:  (по х1)

(по х1)

Сокращенная дизъюнктивная форма логической функции:

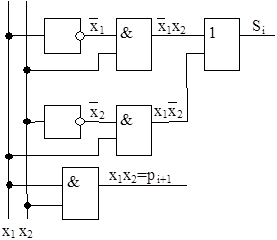

Таким образом, полный сумматор оказывается устройством с двумя выходами и реализуется двумя логическими функциями Si и Pi+1 с тремя аргументами x1, x2, P i.

Схему, реализующую несколько функций, можно представить как простое объединение схем, реализующих каждую функцию отдельно.

Функциональная схема в логическом базисе И, ИЛИ, НЕ на рис.5.10.

Рис.5.10 Функциональная схема полного одноразрядного сумматора.

Но такой путь, как правило, является неэкономичным. Схема оказалась реализованной на 16 базовых логических элементах.

Часто бывает целесообразно преобразовать совокупность данных логических функций к такому виду, чтобы реализующие их схемы содержали общие части, а схема с многими выходами представляла собой единое целое.

Поэтому продолжим преобразования.

На следующем этапе преобразований целесообразно более простую реализацию функции  использовать в качестве составной части другой функции

использовать в качестве составной части другой функции  . Для такой функции табл.5.13.

. Для такой функции табл.5.13.

Таблица 5.13

Таблица истинности полного одноразрядного сумматора

|

|

|

|

|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | ´ |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | ´ |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | ´ |

| 0 | 1 | 1 | 0 | ´ |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | ´ |

| 1 | 0 | 1 | 0 | ´ |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | ´ |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | ´ |

| 1 | 1 | 1 | 1 | 1 |

Но таблица истинности для  теперь содержит избыточные наборы переменных, которые отмечены крестиками ´, т.е. функция оказывается частично (не полностью) определенной. Используем для минимизации частично определенной функции

теперь содержит избыточные наборы переменных, которые отмечены крестиками ´, т.е. функция оказывается частично (не полностью) определенной. Используем для минимизации частично определенной функции  карту Карно (рис.5.11).

карту Карно (рис.5.11).

| 00 | 01 | 11 | 10 |

| 00 |  1 1

|  ´ ´

| 1 | |

| 01 | ´ | ´ | ´ | |

| 11 | ´ |  1 1

| ||

| 10 |  1 1

|  ´ ´

|  ´ ´

| ´ |

Рис.5.11 Карта Карно.

Минимальному покрытию соответствует логическая функция:

После вынесения за скобки  получают подготовленную для реализации логическую функцию:

получают подготовленную для реализации логическую функцию:

Функциональная схема для этой логической функции в логическом базисе И, ИЛИ, НЕ показана на рис. 5.12.

Рис.5.12 Минимизированная функциональная схема полного одноразрядного сумматора.

Схема оказалась реализованной на 9 базовых логических элементах, что почти в два раза меньше, чем в первой схеме. Это подтверждает целесообразность проведенных преобразований.

Для реализации схемы в базисах И-НЕ и ИЛИ-НЕ следует для логической функции применить формулу Де Моргана.

Получены схемы полных одноразрядных сумматоров.

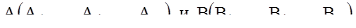

Полные многоразрядные двоичные сумматоры составляются из одноразрядных.

Способов выполнения сложения многоразрядных чисел два: параллельный и последовательный.

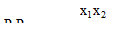

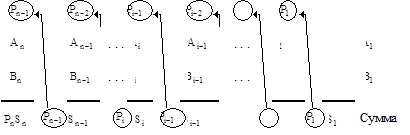

Процедуру сложения двух n-разрядных двоичных чисел  можно представить рис.5.13.

можно представить рис.5.13.

Рис.5.13 Процедура сложения двух n -разрядных двоичных чисел

В младшем разряде сумматора используется полусумматор (два входа для  и

и  ).

).

Начиная со второго разряда необходимо иметь три входа: два для слагаемых  и

и  и один для сигнала переноса

и один для сигнала переноса  с предыдущего разряда, т.е. необходимо применять полный сумматор.

с предыдущего разряда, т.е. необходимо применять полный сумматор.

Введем обозначения:

1) полного сумматора рис.5.14

Рис.5.14 Обозначение на схеме полного сумматора

где S-выход суммы;

- выход переноса;

- выход переноса;