|

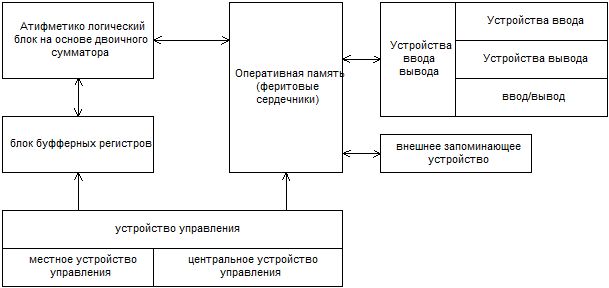

Структурная схема машин I и II поколения.

|

|

|

|

|

Основная цель – повысить производительность.

1) n - разрядный быстродействующий двоичный сумматор (параллельный со схемой сквозного переноса, параллельный перенос) Fоп=2,МГц

2) работа с ВСД числами (десятичная арифметика)

Все управление аппаратным путем делилось на местное (АЛУ, память и др.) и центральное – управление последовательностью выборки команд и выполнение программ, управление системой памяти.

Программист сам распределял память.

Обмен с внешними устройствами реализовался программным способом. Только к концу II поколения появился прямой доступ к памяти (ПДП контроллеры), что явилось колоссальным сдвигом по быстродействию.

32 разряда – максимум (оптимум) для того класса машин.

Структурная схема машин III поколения.

L,R – 4х разрядные регистры используемые для сдвига.

ФК – формирователь кода, передающий код без изменения, инвертирующий разряды, блокирующий передачу и меняющий байты местами.

ПР – признак результата (двухразрядный код).

Регистры: 1-n –рабочие, С1-Сn – регистры состояния и управления (либо целостные регистры, либо некоторое множество триггеров, условно названных как регистры), ССП(PSW) – слово состояния программы или процесса (в конце счетчик адреса команд).

СК – селекторный канал (селекторный процессор).

Байт МК – байт мультиплексный канал (процессор).

Блок МК - блок мультиплексный канал (процессор).

УПУ – управление периферийными устройствами.

УВВ – устройство ввода/вывода.

АКК – адаптер канал-канал

ТСУД – телеметрические средства удаленного доступа.

Была введена четырех фазная синхронизация. Вся работа системы синхронизировалась от единого генератора. В одном такте процессора 4 фазы. Все операции реализуются на двоичном сумматоре. Структура процессора имеет конвейерный тип. Одновременно выполняется трех уровневое совмещение команд. Операции с плавающей точкой реализуются для шестнадцатиричной системы счисления (q=16), с фиксированной точкой – двоичная система.

|

|

|

Регистровое ЗУ введено 1) для обращения с сокращенными (4-х разрядными) адресами; 2) регистровое ЗУ быстрее оперативной памяти. РЗУ состоит из 24 регистров (32-х разрядных) из которых 16 называют РОН (регистры общего назначения), используемые для выполнения операций с фиксированной точкой, логических, а так же для хранения компонент исполнительного адреса индекса и базы. 8 регистров объединяются попарно и образуют 4 (64-х разрядных) регистра с плавающей точкой.

Основная память используется для хранения команд и данных, с которыми работают арифметико-логический блок и каналы ввода-вывода. ОП отличается в машинах разного типа емкостью и разрядностью слов (4,8,16 байт). В ранних моделях регистровое ЗУ было реализовано логически в начальных ячейках оперативной памяти.

В структуре машин III поколения значительно улучшен обмен с внешними устройствами. Для этих целей введены каналы (процессоры) ввода/вывода. Появились команды ввода/вывода. При обмене данными центральный процессор выдает команду в канал и в дальнейшем эту команду выполняет сам канал. Каждый канал имеет свою систему команд. Селективный канал служит для обмена с быстродействующими внешними устройствами (обмен селективный). Байт мультиплексный канал осуществляет обмен с медленными внешними устройствами, но со всеми сразу, по очереди. Имеет внутренние регистры для обмена с устройствами, которые называют подканалами. Блок мультиплексный канал –обмен блоков байтов, а функции те же. Для сокращения времени при передаче между УВВ на разных каналах используются специальные адаптеры канал-канал. Для работы с компьютером на расстоянии от 100м. до 50км. Используют специальные телеметрические средства удаленного доступа.

|

|

|