|

Структурные схемы ЦВМ IV поколения.

|

|

|

|

|

1) Реализовано на микропроцессорах. Основная масса на базе однокристальных микропроцессоров и их структурная схема совпадала со структурой схемой малых ЭВМ.

ПКПП – программируемый контроллер приоритетных прерываний.

ПКПДП - программируемый контроллер прямого доступа к памяти.

ПП – подсистема памяти.

УВВ – устройства ввода/вывода.

К данному типу принадлежат ЦВМ на базе i8080А – popular computer, 8-ми разрядный. Позднее появился i8085 – добавлены операции деления и умножения (использовался как контроллер). Z80 –побитная обработка информации (ZX Spectrum). i8086/88 – 13 августа 1981 года выпущен первый IBM PC XT. Далее появились IBM PC AT.

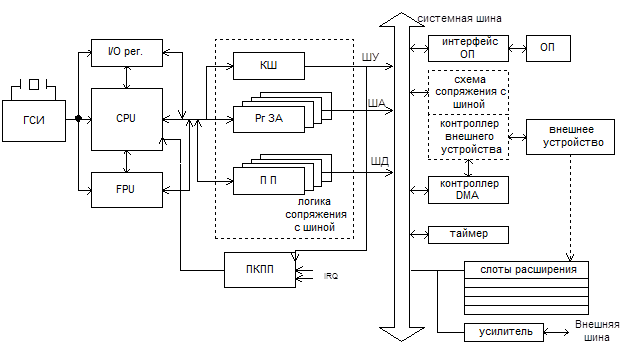

4. Структурная схема IBM PC XT.

ГСИ – генератор синхроимпульсов.

КШ – контроллер шины.

РгЗА – регистры защелки адреса.

ПП – подсистема памяти.

ШУ – шина управления.

ША – шина адреса.

ШД – шина данных.

ПКПП – программируемый контроллер приоритетных прерываний.

ГСИ, КШ, РгЗА, ПП, ПКПП, контроллер DMA, таймер, и т.д. образуют все вместе так называемый набор чипов (CHIPSET).

|

5. Структурная схема IBM PC AT.

Основной недостаток – удаленность оперативной памяти по шинам от процессора, в связи с этим снижение скорости обмена процессор – память.

i386 – ввели буферную память КЭШ и был введен контроллер кэша. Структурная схема стала иметь следующий вид:

4) Традиционная структурная схема ЦВМ IV поколения с КЭШ.

Для i386 КЭШ – внешние, навесные вошли в структуру ChipSet. Начиная с 486 появилось 2 уровня: 1) внутри кристалла процессора (8 кбайт); 2) расширенный КЭШ второго уровня на системной плате. Для процессоров Pentium 2 характерно то, что КЭШ второго уровня размещается на плате процессора, а не на системной плате или внутри процессора. У процессоров CeleronA(128к) КЭШ работает на частоте процессора.

|

|

|

Узким местом для данной конфигурации становится графика и работа с жестким диском.

|

|

6. ЦВМ с локальной шиной.

Этот вариант хорошо зарекомендовал себя как вычислительный модуль мультипроцессорной системы. Системная шина использовалась для сопряжения с другими модулями через арбитр шины, а локальная шина использовалась для подключения локальных устройств ввода/вывода и взаимодействия пользователя и внешних устройств с этим модулем. Серверы использовали именно такую конфигурацию.

Основной недостаток – скорость обмена с жестким диском была в норме, а но отставала графика. Появилась 3-х мерная графика, реализуемая в реальном масштабе времени, динамические изображения в виртуальном пространстве. Все это привело к необходимости ускорения графики.

7. Структурная схема с локальной шиной VESA.

1992г. – официальное появление шины VLB (vesa local bus).

Источник питания –3,3 вольт. Шина данных – 32 и 64 разряда. Тактовая частота – 33 и 50 МГц. Арбитража по шине нет. На частоте 33МГц скорость обмена 66 Мб/сек. Позволяла подключать 2 или 3 устройства.

|

8) структурная схема с шиной PCI (1992г.)

|

У шины PCI есть арбитраж устройств. Версии 1.0 и 2.0: нагрузочная способность до 10 устройств; прерывания не по фронту, а по уровню; введена пакетная обработка данных по шине; частота 33 МГц; источники питания 5V и 3.3V; шина данных 1.0 - 32-х, 2.0 – 64-х разрядные; скорость обмена 132 Мбайт/сек для 1.0 и 264 Мбайт/сек для 2.0.

PCI версии 2.1 работала с процессором 100МГц и выше; тактовые частоты – 33 и 66 МГц; скорость обмена – 520 Мбайт/сек.

Дальнейшее развитие привело к схемам с AGP (advanced graphic port) и USB (universal serial bus). Появился также контроллер SCSI, который имеет возможность общаться с несколькими устройствами одновременно – аналог мультиплексорного канала машин III поколения.

|

|

|

Другие направления связаны со мультипроцессорными конфигурациями и мультикомпьютерными (multiputer) вычислительными комплексами на базе вычислительных модулей.

Пятое поколение ЦВМ реализовано в структурных схемах 7, в которых появилась аппаратная возможность обработки видео и звуковой информации.

|

|

|